# High Performance Computing Systems: Status and Outlook

J.J. Dongarra

University of Tennessee

and

Oak Ridge National Laboratory

and

University of Manchester

dongarra@eecs.utk.edu

A.J. van der Steen

NCF/HPC Research

L.J. Costerstraat 5

6827 AR Arnhem

The Netherlands

steen@hpcresearch.nl

## CONTENTS

| 1          | Introduction                                | 1  |

|------------|---------------------------------------------|----|

| 2          | The main architectural classes              | 2  |

| 3          | Shared-memory SIMD machines                 | 6  |

| 4          | Distributed-memory SIMD machines            | 8  |

| 5          | Shared-memory MIMD machines                 | 10 |

| 6          | Distributed-memory MIMD machines            | 13 |

| 7          | ccNUMA machines                             | 17 |

| 8          | Clusters                                    | 18 |

| 9          | Processors                                  | 20 |

| 10         | Computational accelerators                  | 38 |

| 11         | Networks                                    | 53 |

| 12         | Recent Trends in High Performance Computing | 59 |

| 13         | HPC Challenges                              | 72 |

| References |                                             | 91 |

#### 1. Introduction

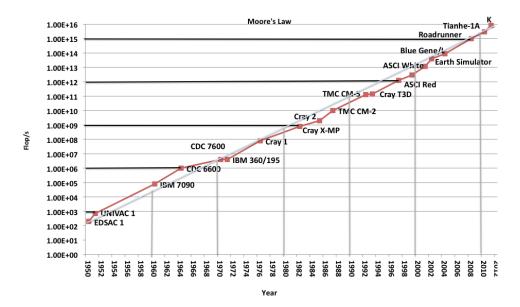

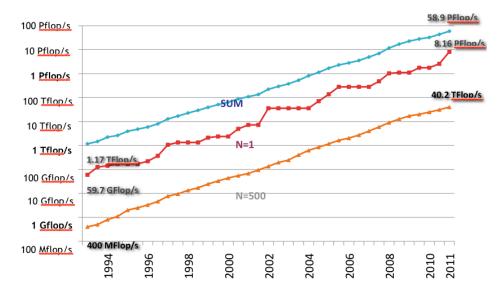

High Performance computer systems can be regarded as the most powerful and flexible research instruments today. They are employed to model phenomena in fields so various as climatology, quantum chemistry, computational medicine, High-Energy Physics and many, many other areas. In

this article we present some of the architectural properties and computer components that make up the present HPC computers and also give an outlook on the systems to come. For even though the speed of computers has increased tremendously over the years (often a doubling in speed every 2 or 3 years), the need for ever faster computers is still there and will not disappear in the forseeable future.

Before going on to the descriptions of the machines themselves, it is useful to consider some mechanisms that are or have been used to increase the performance. The hardware structure or architecture determines to a large extent what the possibilities and impossibilities are in speeding up a computer system beyond the performance of a single CPU core. Another important factor that is considered in combination with the hardware is the capability of compilers to generate efficient code to be executed on the given hardware platform. In many cases it is hard to distinguish between hardware and software influences and one has to be careful in the interpretation of results when ascribing certain effects to hardware or software peculiarities or both. In this article we will give most emphasis on the hardware architecture. For a description of machines that can be classified as "high-performance" one is referred to (?) or (?).

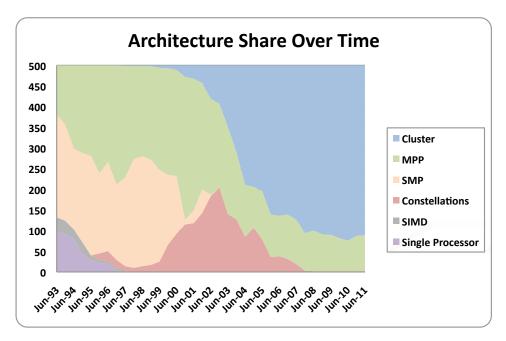

The rest of the paper is organized as follows: Section 2 discusses the main architectural classification of high-performance computers; Section 3 presents shared-memory vector SIMD machines; Section 4 discusses distributed-memory SIMD machines; Section 5 looks at shared-memory MIMD machines; Section 6 overviews the distributed-memory MIMD machines; Section 7 ccNUMA machines which are closely related to shared-memory systems; Section 8 presents clusters; Section 9 overviews processors and looks at what's currently available today; Section 10 presents computational accelerators, GPUs, and FPGAs; Section 11 discusses networks and what is commercially available; Section 12 overviews recent trends in high-performance computing; Section 13 concludes with an examination of some of the challenges we face in the effective use of high-performance computers.

#### 2. The main architectural classes

For many years, the taxonomy of Flynn (?) has proven to be useful for the classification of high-performance computers. This classification is based on the way of manipulating of instruction and data streams and comprises four main architectural classes. We will first briefly sketch these classes and afterwards fill in some details when each of the classes is described separately.

— SISD machines: These are the conventional systems that contain one CPU and hence can accommodate one instruction stream that is executed serially. Nowadays about all large servers have more than one CPU but each of these execute instruction streams that are unrelated. Therefore, such systems should still be regarded as (a couple of) SISD machines acting on different data spaces. Examples of SISD machines are for instance workstations as offered by many vendors. The definition of SISD machines is given here for completeness' sake. We will not discuss this type of machines in this report.

SIMD machines: Such systems often have a large number of processing units, that all may execute the same instruction on different data in lock-step. So, a single instruction manipulates many data items in parallel. Examples of SIMD machines in this class were the CPP Gamma II and the Quadrics Apemille, which are not marketed anymore. Nevertheless, the concept is still interesting and it is recurring these days as a co-processor in HPC systems, albeit in a somewhat restricted form in some computational accelerators like GPUs.

Another subclass of the SIMD systems are the vectorprocessors. Vectorprocessors act on arrays of similar data rather than on single data items using specially structured CPUs. When data can be manipulated by these vector units, results can be delivered with a rate of one, two and — in special cases — of three per clock cycle (a clock cycle being defined as the basic internal unit of time for the system). So, vector processors execute on their data in an almost parallel way but only when executing in vector mode. In this case they are several times faster than when executing in conventional scalar mode. For practical purposes vectorprocessors are therefore mostly regarded as SIMD machines. Examples of such systems are for instance the NEC SX-9B and the Cray X2.

- MISD machines: Theoretically in these types of machines multiple instructions should act on a single stream of data. As yet no practical machine in this class has been constructed nor are such systems easy to conceive. We will disregard them in the following discussions.

- MIMD machines: These machines execute several instruction streams in parallel on different data. The difference with the multi-processor SIMD machines mentioned above lies in the fact that the instructions and data are related because they represent different parts of the same task to be executed. So, MIMD systems may run many sub-tasks in parallel in order to shorten the time-to-solution for the main task to be executed. There is a large variety of MIMD systems and especially in this class the Flynn taxonomy proves to be not fully adequate for the classification of systems. Systems that behave very differently like a 4-processor NEC SX-9 vector system and a 100,000-processor IBM BlueGene/P both fall in this class. In the following we will make another important distinction between classes of systems and treat them accordingly.

- Shared-memory systems: Shared-memory systems have multiple

CPUs, all of which share the same address space. This means that the knowledge of where data is stored is of no concern to the user as there is only one memory accessed by all CPUs on an equal basis. Shared memory systems can be both SIMD or MIMD. Single-CPU vector processors can be regarded as an example of the former, while the multi-CPU models of these machines are examples of the latter. We will sometimes use the abbreviations SM-SIMD and SM-MIMD for the two subclasses.

Distributed-memory systems: In this case each CPU has its own associated memory. The CPUs are connected by some network and may exchange data between their respective memories when required. In contrast to shared-memory machines the user must be aware of the location of the data in the local memories and will have to move or distribute these data explicitly when needed. Again, distributed-memory systems may be either SIMD or MIMD. The first class of SIMD systems mentioned which operate in lock step, all have distributed memories associated to the processors. As we will see, distributed-memory MIMD systems exhibit a large variety in the topology of their interconnection network. The details of this topology are largely hidden from the user which is quite helpful with respect to portability of applications but that may have an impact on the performance. For the distributed-memory systems we will sometimes use DM-SIMD and DM-MIMD to indicate the two subclasses.

As already alluded to, although the difference between shared and distributedmemory machines seems clear cut, this is not always the case from the user's point of view. For instance, the late Kendall Square Research systems employed the idea of "virtual shared-memory" on a hardware level. Virtual shared-memory can also be simulated at the programming level: A specification of High Performance Fortran (HPF) was published in 1993 (?) which, by means of compiler, directives distributes the data over the available processors. Therefore, the system on which HPF is implemented in this case will look like a shared-memory machine to the user. Other vendors of Massively Parallel Processing systems (sometimes called MPP systems), like SGI, also support proprietary virtual shared-memory programming models due to the fact that these physically distributed memory systems are able to address the whole collective address space. So, for the user, such systems have one global address space spanning all of the memory in the system. We will say a little more about the structure of such systems in section??. In addition, packages like TreadMarks ((?)) provide a "distributed shared-memory" environment for networks of workstations. A good overview of such systems is given at (?). Since 2006 Intel has marketed its "Cluster OpenMP" (based

on TreadMarks) as a commercial product. It allows the use of the shared-memory OpenMP parallel model (?) to be used on distributed-memory clusters. For the last few years companies like ScaleMP and 3Leaf have provided products to aggregate physical distributed memory into virtual shared memory.

Lastly, so-called Partitioned Global Address Space (PGAS) languages like Co-Array Fortran (CAF) and Unified Parallel C (UPC) are gaining popularity due to the recently emerging multi-core processors. With proper implementation this allows a global view of the data and one has language facilities that make it possible to specify processing of data associated with a (set of) processor(s) without the need for explicitly moving the data around.

Distributed processing takes the DM-MIMD concept one step further: instead of many integrated processors in one or several boxes, workstations, mainframes, etc., are connected by (Gigabit) Ethernet, or other, faster networks and set to work concurrently on tasks in the same program. Conceptually, this is not different from DM-MIMD computing, but the communication between processors can be much slower. Packages that initially were made to realise distributed computing like PVM (standing for Parallel <u>Virtual Machine</u>) (?), and MPI (<u>Message Passing Interface</u>, (?), (?)) have become de facto standards for the "message passing" programming model. MPI and PVM have become so widely accepted that they have been adopted by all vendors of distributed-memory MIMD systems and even on sharedmemory MIMD systems for compatibility reasons. In addition, there is a tendency to cluster shared-memory systems by a fast communication network to obtain systems with a very high computational power. E.g., the NEC SX-9, and the Cray X2 have this structure. So, within the clustered nodes a shared-memory programming style can be used while between clusters message-passing should be used. It must be said that PVM is not used very much anymore and the development has stopped. MPI has now more or less become the de facto standard.

For SM-MIMD systems we mention OpenMP (?),

(?), (?), that can be used to parallelise Fortran and C(++) programs by inserting comment directives (Fortran 77/90/95) or pragmas (C/C++) into the code. OpenMP has quickly been adopted by all major vendors and has become a well established standard for shared memory systems.

Note, however, that for both MPI-2 and OpenMP 2.5, the latest standards, many systems/compilers only implement a part of these standards. One has to therefore inquire carefully whether a particular system has the full functionality of these standards available. The standard vendor documentation will almost never be clear on this point.

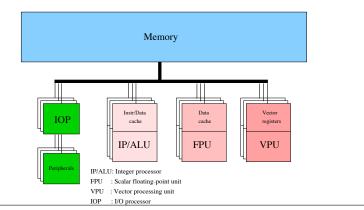

Figure 3.1. Blockdiagram of a vector processor.

### 3. Shared-memory SIMD machines

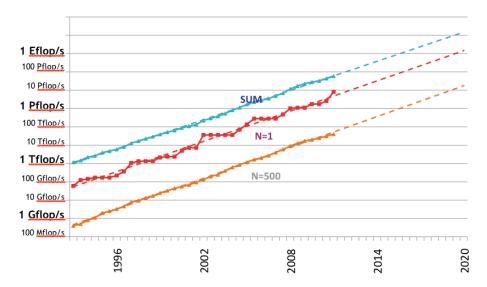

This subclass of machines is practically equivalent to the single-processor vector processors, although other interesting machines in this subclass have existed (viz. VLIW machines (?)) and may emerge again in the near future. In the block diagram in Figure ?? we depict a generic model of a vector architecture. The single-processor vector machine will have only one of the vector processors shown here and the system may even have its scalar floating-point capability shared with the vector processor (as was the case in some Cray systems). It may be noted that the VPU does not show a cache. Vectorprocessors may have a cache but in many cases the vector unit cannot take advantage of it and execution speed may in some cases even be unfavourably affected because of frequent cache overflow. Of late, however, this tendency is reversed because of the increasing gap in speed between the memory and the processors: the Cray X2 has a cache and NEC's SX-9 vector system has a facility that is somewhat like a cache.

Although vector processors have existed that loaded their operands directly from memory and stored the results again immediately in memory (CDC Cyber 205, ETA-10), present-day vector processors use vector registers. This impairs the speed of operations while providing much more flexibility in gathering operands and manipulation with intermediate results.

Because of the generic nature of Figure ?? no details of the interconnection between the VPU and the memory are shown. Still, these details are very important for the effective speed of a vector operation: when the bandwidth between memory and the VPU is too small it is not possible to take full advantage of the VPU because it has to wait for operands and/or has to wait before it can store results. When the ratio of arithmetic to load/store operations is not high enough to compensate for such situations, severe performance losses may be incurred. The influence of the number of load/store

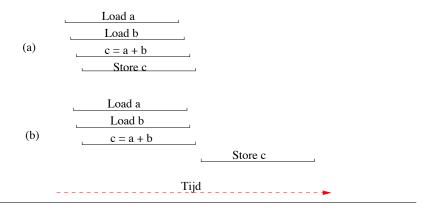

Figure 3.2. Schematic diagram of a vector addition. Case (a) when two load- and one store pipe are available; case (b) when two load/store pipes are available.

paths for the dyadic vector operation c = a + b (a, b, and c) vectors) is depicted in Figure ??. Because of the high costs of implementing these data paths between memory and the VPU, often compromises are sought and the full required bandwidth (i.e., two load operations and one store operation at the *same* time) is seldom relized. Only Cray Inc. in its former Y-MP, C-series, and T-series employed this very high bandwidth. Vendors now rely on additional caches and other tricks to hide the lack of bandwidth.

The VPUs are shown as a single block in Figure ??. Yet, there is a considerable diversity in the structure of VPUs. Every VPU consists of a number of vector functional units, or "pipes" that fulfill one or several functions in the VPU. Every VPU will have pipes that are designated to perform memory access functions, thus assuring the timely delivery of operands to the arithmetic pipes and of storing the results in memory again. Usually there will be several arithmetic functional units for integer/logical arithmetic, for floating-point addition, for multiplication and sometimes a combination of both, a so-called compound operation. Division is performed by an iterative procedure, table look-up, or a combination of both using the add and multiply pipe. In addition, there will almost always be a mask pipe to enable operation on a selected subset of elements in a vector of operands. Lastly, such sets of vector pipes can be replicated within one VPU (2 up to 16-fold replication occurs). Ideally, this will increase the performance per VPU by the same factor provided the bandwidth to memory is adequate.

Lastly, it must be remarked that vector processors as described here are not considered a viable economic option anymore and both the Cray X2 and the NEC SX-9 will disappear in the near future: vector units within standard processor cores and computational accelerators have invaded the vector processing area. Although they are less efficient and have bandwidth

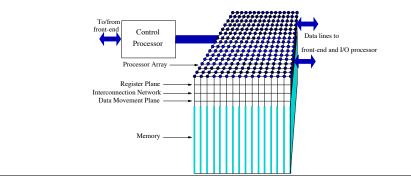

Figure 4.3. A generic block diagram of a distributed-memory SIMD machine.

limitations, they are so much cheaper that the classical vector processors are outcompeted.

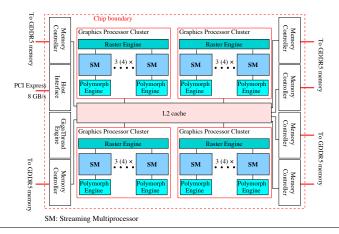

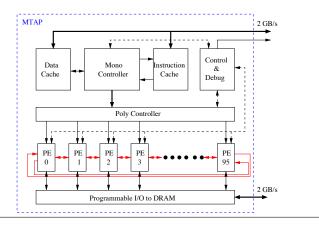

## 4. Distributed-memory SIMD machines

Machines of the DM-SIMD type are sometimes also known as processor-array machines (?). Because the processors of these machines operate in lock-step, i.e., all processors execute the same instruction at the same time (but on different data items), no synchronisation between processors is required. This greatly simplifies the design of such systems. A control processor issues the instructions that are to be executed by the processors in the processor array. Presently, no commercially available machines of the processor-array type are marketed. However, because of the shrinking size of devices on a chip, it may be worthwhile to locate a simple processor with its network components on a single chip thus making processor-array systems economically viable again. In fact, common Graphical Processing Units (GPUs) share many characteristics with processor array systems. This is the reason we still discuss this type of system.

DM-SIMD machines use a front-end processor to which they are connected by a data path to the control processor. Operations that cannot be executed by the processor array or by the control processor are offloaded to the front-end system. For instance, I/O may be through the front-end system, by the processor array machine itself, or by both. Figure ?? shows a generic model of a DM-SIMD machine of which actual models will deviate to some degree. Figure ?? might suggest that all processors in such systems are connected in a 2-D grid and indeed, the interconnection topology of this type of machine always includes the 2-D grid. As opposing ends of each grid line are also always connected, the topology is rather that of a torus. This is not the only interconnection scheme: They might also be connected in 3-D, diagonally, or in more complex structures.

It is possible to exclude processors in the array from executing an instruc-

tion on certain logical conditions, but this means that during the time of this instruction these processors are idle (a direct consequence of the SIMDtype operation) which immediately lowers the performance. Another factor that may adversely affect the speed occurs when data required by processor i resides in the memory of processor j — in fact, as this occurs for all processors at the same time, this effectively means that data will have to be permuted across the processors. To access the data in processor j, the data will have to be fetched by this processor and then sent through the routing network to processor i. This may be fairly time consuming. For both reasons mentioned, DM-SIMD machines are rather specialised in their use when one wants to employ their full parallelism. Generally, they perform excellently on digital signal and image processing, and on certain types of Monte Carlo simulations where virtually no data exchange between processors is required, and exactly the same type of operations are done on massive data sets with a size that can be made to fit comfortably in these machines. They will also perform well on gene-matching type of applications.

The control processor as depicted in Figure ?? may be more or less intelligent. It issues the instruction sequence that will be executed by the processor array. In the worst case (that means a less autonomous control processor) when an instruction is not fit for execution on the processor array (e.g., a simple print instruction) it might be offloaded to the front-end processor which may be much slower than execution on the control processor. In the case of a more autonomous control processor this can be avoided thus saving processing interrupts both on the front-end and on the control processor. Most DM-SIMD systems have the ability to handle I/O independently from the front-end processors. This is favourable because the communication between the front-end and back-end systems is avoided. A (specialised) I/O device for the processor-array system is generally much more efficient in providing the necessary data directly to the memory of the processor array. Especially for very data-intensive applications like radar and image processing such I/O systems are very important.

A feature that is peculiar to this type of machines is that the processors are sometimes of a very simple bit-serial type, i.e., the processors operate on the data items bit-wise, irrespective of their type. So, e.g., operations on integers are produced by software routines on these simple bit-serial processors which takes at least as many cycles as the operands are long. So, a 32-bit integer result will be produced two times faster than a 64-bit result. For floating-point operations a similar situation holds, be it that the number of cycles required is a multiple of that needed for an integer operation. As the number of processors in this type of system is mostly large (1024 or larger, the Quadrics Apemille was a notable exception, however), the slower operation on floating-point numbers can be often compensated for by their number, while the cost per processor is quite low as compared to full floating-point

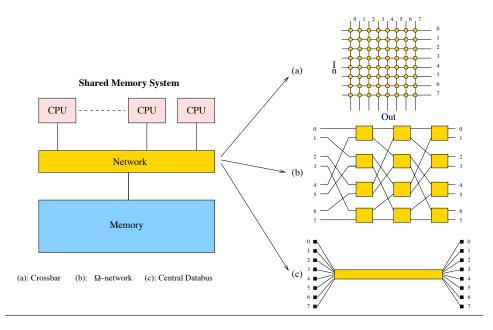

Figure 5.4. Some examples of interconnection structures used in shared-memory MIMD systems.

processors. In some cases, however, floating-point co-processors were added to the processor-array. Their number was 8–16 times lower than that of the bit-serial processors because of the cost argument. An advantage of bit-serial processors is that they may operate on operands of any length. This is particularly advantageous for random number generation (which often boils down to logical manipulation of bits) and for signal processing because in both cases operands of only 1–8 bits are abundant. because, as mentioned, the execution time for bit-serial machines is proportional to the length of the operands, this may result in significant speedups.

Presently there are no DM-SIMD systems on the market but some types of computational accelerators (see section ??) share many characteristics with DM-SIMD systems that have existed until shortly. We will briefly discuss some properties of these accelerators later.

### 5. Shared-memory MIMD machines

In Figure ?? already one subclass of this type of machines was shown. In fact, the single-processor vector machine discussed there was a special case of a more general type. The figure shows that more than one FPU and/or VPU may be possible in one system.

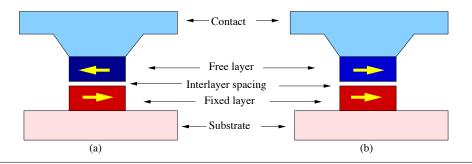

The main problem one is confronted with in shared-memory systems is that of the connection of the CPUs to each other and to the memory. As more CPUs are added, the collective bandwidth to the memory ideally should increase linearly with the number of processors, while each processor should preferably communicate directly with all others without the much slower alternative of having to use the memory in an intermediate stage. Unfortunately, full interconnection is quite costly, growing with  $\mathcal{O}(n^2)$  while increasing the number of processors with  $\mathcal{O}(n)$ . So, various alternatives have been tried. Figure ?? shows some of the interconnection structures that are (and have been) used.

As can be seen from the Figure, a crossbar uses  $n^2$  connections, an  $\Omega$ -network uses  $n\log_2 n$  connections while with the central bus there is only one connection. This is reflected in the use of each connection path for the different types of interconnections: for a crossbar each data path is direct and does not have to be shared with other elements. In case of the  $\Omega$ -network there are  $\log_2 n$  switching stages and as many data items may have to compete for any path. For the central data bus all data have to share the same bus, so n data items may compete at any time.

The bus connection is the least expensive solution, but it has the obvious drawback that bus contention may occur, thus slowing down the computations. Various intricate strategies have been devised using caches associated with the CPUs to minimise the bus traffic. This leads however to a more complicated bus structure which raises the costs. In practice it has proved to be very hard to design buses that are fast enough, especially where the speed of the processors has been increasing very quickly and it imposes an upper bound on the number of processors thus connected that in practice appears not to exceed a number of 10-20. In 1992, a new standard (IEEE P896) for a fast bus to connect either internal system components or to external systems was defined. This bus, called the Scalable Coherent Interface (SCI) provides a point-to-point bandwidth of 200-1,000 MB/s. It has been used in the HP Exemplar systems, but also within a cluster of workstations as offered by SCALI. The SCI is much more than a simple bus and it can act as the hardware network framework for distributed computing, see (?). It has now been effectively superseded by InfiniBand, however (see section ??).

A multi-stage crossbar is a network with a logarithmic complexity and it has a structure which is situated somewhere in between a bus and a crossbar with respect to potential capacity and costs. The  $\Omega$ -network as depicted in Figure ?? is an example. Commercially available machines like the IBM eServer p575, the SGI Altix UV, and many others use(d) such a network structure, but a number of experimental machines also have used this or a similar kind of interconnection. The BBN TC2000 that acted as a virtual shared-memory MIMD system used an analogous type of network (a Butterfly-network) and it is likely that new machines will use it, especially as the number of processors grows. For a large number of processors the  $n \log_2 n$

connections quickly become more attractive than the  $n^2$  used in crossbars. Of course, the switches at the intermediate levels should be sufficiently fast to cope with the bandwidth required. Obviously, not only the *structure* but also the *width* of the links between the processors is important: a network using 16-bit parallel links will have a bandwidth which is 16 times higher than a network with the same topology implemented with serial links.

Until recently multi-processor vectorprocessors used crossbars. This was feasible because the maximum number of processors within in a system node was small (16 at most). In the late Cray X2 the number of processors had increased so much, however, that it had to change to a logarithmic network topology (see section ??). It not only becomes harder to build a crossbar of sufficient speed for the larger numbers of processors, the processors themselves generally also increase in speed individually, doubling the problems of making the speed of the crossbar match that of the bandwidth required by the processors.

Whichever network is used, the type of processors in principle could be arbitrary for any topology. In practice, however, bus structured machines cannot support vector processors as the speeds of these would grossly mismatch with any bus that could be constructed with reasonable costs. All available bus-oriented systems use RISC processors as far as they still exist. The local caches of the processors can sometimes alleviate the bandwidth problem if the data access can be satisfied by the caches thus avoiding references to the memory.

The systems discussed in this subsection are of the MIMD type and therefore different tasks may run on different processors simultaneously. In many cases synchronisation between tasks is required and again the interconnection structure is very important here. Some Cray vectorprocessors in the past employed special communication registers within the CPUs (the X-MP and Y-MP/C series) by which they could communicate directly with the other CPUs they have to synchronise with. This is, however, not practised anymore as it is viewed too costly a feature. The systems may also synchronise via the shared memory. Generally, this is much slower but it can still be acceptable when the synchronisation occurs relatively seldom. Of course, in bus-based systems communication also has to be done via a bus. This bus is mostly separated from the data bus to ensure a maximum speed for the synchronisation.

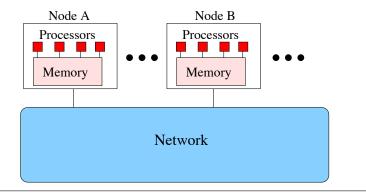

#### 6. Distributed-memory MIMD machines

The class of DM-MIMD machines represents undoubtedly the largest fraction in the family of high-performance computers. A generic diagram is given in Figure ??. The figure shows that within a computational node A, B, etc., a number of processors (four in this case) draw on the same local

Figure 6.5. Generic diagram of a DM-MIMD machine.

memory and that the nodes are connected by some network. Consequently, when a processor in node A needs data present in node B this has to be accessed through the network. Hence the characterisation of the system as being of the distributed memory type. The vast majority of all HPC systems today are a variation of the model shown in Figure ??.

This type of machines is more difficult to deal with than shared-memory machines and DM-SIMD machines. The latter type of machines are processor-array systems in which the data structures that are candidates for parallelisation are vectors and multi-dimensional arrays that are laid out automatically on the processor array by the system software. For shared-memory systems the data distribution is completely transparent to the user. This is generally quite different for DM-MIMD systems where the user has to distribute the data over the processors, and also the data exchange between processors has to be performed explicitly when using the so-called message passing parallelisation model (which is the case in the vast majority of programs). The initial reluctance to use DM-MIMD machines seems to have decreased. This is partly due to the now existing standard for communication software ((?, ?, ?)) and partly because, at least theoretically, this class of systems is able to outperform all other types of machines.

Alternatively, instead of message passing, a Partitioned Global Address Space parallelisation model may be used with a programming language like UPC (?) or Co-Array Fortran (?). In this case one still has to be aware where the relevant data are, but no explicit sending/receiving between processors is necessary. This greatly simplifies the programming but the compilers are still either fairly immature or even in an experimental stage which does not always guarantee a great performance to say the least.

The advantages of DM-MIMD systems are clear: the bandwidth problem that haunts shared-memory systems is avoided because the bandwidth scales up automatically with the number of processors. Furthermore, the speed of the memory which is another critical issue with shared-memory systems (to get a peak performance that is comparable to that of DM-MIMD systems, the processors of the shared-memory machines should be very fast and the speed of the memory should match it) is less important for the DM-MIMD machines, because more processors can be configured without the aforementioned bandwidth problems.

Of course, DM-MIMD systems also have their disadvantages: The communication between processors is slower than in SM-MIMD systems, and so, the synchronisation overhead, in the case of communicating tasks, is generally orders of magnitude higher than in shared-memory machines. Moreover, the access to data that are not in the local memory belonging to a particular processor have to be obtained from non-local memory (or memories). This again is very slow compared to local data access. When the structure of a problem dictates a frequent exchange of data between processors and/or requires many processor synchronisations, it may well be that only a very small fraction of the theoretical peak speed can be obtained. As already mentioned, the data and task decomposition are factors that mostly have to be dealt with explicitly, which may be far from trivial.

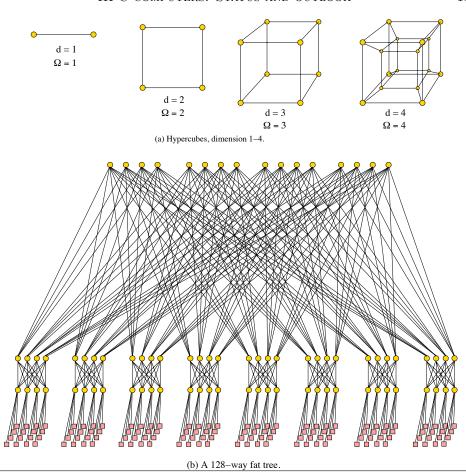

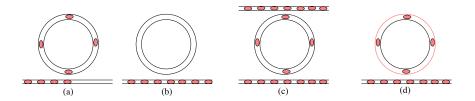

It will be clear from the paragraph above that also for DM-MIMD machines both the topology and the speed of the data paths are crucial for the practical usefulness of a system. Again, as in the section on SM-MIMD systems, the richness of the connection structure has to be balanced against the costs. Of the many conceivable interconnection structures, only a few are popular in practice. One of these is the so-called hypercube topology as depicted in Figure ?? (a).

A nice feature of the hypercube topology is that for a hypercube with  $2^d$ nodes the number of steps to be taken between any two nodes is at most d. So, the dimension of the network grows only logarithmically with the number of nodes. In addition, theoretically, it is possible to simulate any other topology on a hypercube: trees, rings, 2-D and 3-D meshes, etc. In practice, the exact topology for hypercubes does not matter too much anymore because all systems in the market today employ what is called "wormhole routing" or variants thereof. This means that a message is sent from node i to node j, a header message is sent from i to j, resulting in a direct connection between these nodes. As soon as this connection is established, the proper data is sent through this connection without disturbing the operation of the intermediate nodes. Except for a small amount of time in setting up the connection between nodes, the communication time has become fairly independent of the distance between the nodes. Of course, when several messages in a busy network have to compete for the same paths, waiting times are incurred as in any network that does not directly connect any processor to all others and often rerouting strategies are employed to circumvent busy links if the connecting network supports it. Also the network

Figure 6.6. Some often used networks for DM machine types.

nodes themselves have become quite powerful and, depending on the type of network hardware may send and rerout message packages in a way that minimises contention.

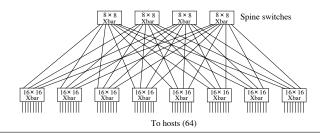

Another cost-effective way to connect a large number of processors is by means of a  $fat\ tree$ . In principle a simple tree structure for a network is sufficient to connect all nodes in a computer system. However, in practice it turns out that, near the root of the tree, congestion occurs because of the concentration of messages that first have to traverse the higher levels in the tree structure before they can descend again to their target nodes. The fat tree amends this shortcoming by providing more bandwidth (mostly in the form of multiple connections) in the higher levels of the tree. One speaks of a N-ary fat tree when the levels towards the roots are N times the number of connections in the level below it. An example of a quaternary fat tree

with a bandwidth in the highest level that is four times that of the lower levels is shown in Figure ?? (b).

A number of massively parallel DM-MIMD systems seem to favour a 2or 3-D mesh (torus) structure. The rationale for this seems to be that most large-scale physical simulations can be mapped efficiently on this topology and that a richer interconnection structure hardly pays off. However, some systems maintain (an) additional network(s) besides the mesh to handle certain bottlenecks in data distribution and retrieval (?). Also on IBM's BlueGene systems this philosophy has been followed.

A large fraction of systems in the DM-MIMD class employ crossbars. For relatively small amounts of processors (in the order of 64) this may be a direct or 1-stage crossbar, while to connect larger numbers of nodes multi-stage crossbars are used, i.e., the connections of a crossbar at level 1 connect to a crossbar at level 2, etc., instead of directly to nodes at more remote distances in the topology. In this way it is possible to connect many thousands of nodes through only a few switching stages. In addition to the hypercube structure, other logarithmic complexity networks like Butterfly,  $\Omega$ , or shuffle-exchange networks and fat trees are often employed in such systems.

As with SM-MIMD machines, a node may in principle consist of any type of processor (scalar or vector) for computation or transaction processing together with local memory (with or without cache) and, in almost all cases, a separate communication processor with links to connect the node to its neighbours. Nowadays, the node processors are mostly off-the-shelf RISC processors sometimes enhanced by vector processors. A problem that is peculiar to DM-MIMD systems is the mismatch of communication vs. computation speed that may occur when the node processors are upgraded without also speeding up the intercommunication. In many cases this may result in turning computational-bound problems into communication-bound problems.

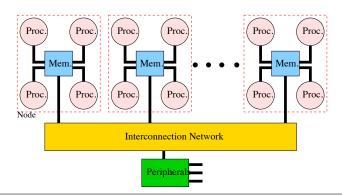

## 7. ccNUMA machines

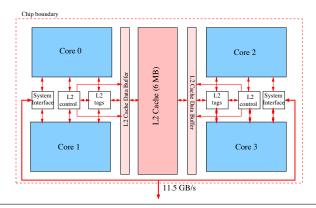

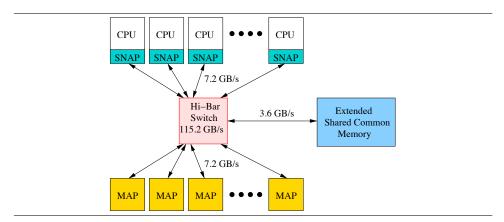

As already mentioned in the introduction, a trend can be observed to build systems that have a rather small (up to 16) number of processors that are tightly integrated in a cluster, a Symmetric Multi-Processing (SMP) node. The processors in such a node are virtually always connected by a 1-stage crossbar while these clusters are connected by a less costly network. Such a system may look as depicted in Figure ??. Note that in Figure ?? all CPUs in a cluster are connected to a common part of the memory. (Figure ?? looks functionally identical to Figure ??, however, there is a difference that cannot be expressed in the figure: all memory is directly accessible by all processors without the necessity to transfer the data explicitly).

Figure 7.7. Block diagram of a system with a "hybrid" network: clusters of four CPUs are connected by a crossbar. The clusters are connected by a less expensive network, e.g., a Butterfly network.

The most important ways to let the SMP nodes share their memory are S-COMA (Simple Cache-Only Memory Architecture) and ccNUMA, which stands for Cache Coherent Non-Uniform Memory Access. Therefore, such systems can be considered as SM-MIMD machines. On the other hand, because the memory is physically distributed, it cannot be guaranteed that a data access operation always will be satisfied within the same time. In S-COMA systems the cache hierarchy of the local nodes is extended to the memory of the other nodes. So, when data is required that does not reside in the local node's memory it is retrieved from the memory of the node where it is stored. In ccNUMA this concept is further extended in that all memory in the system is regarded (and addressed) globally. So, a data item may not be physically local but logically it belongs to one shared address space. Because the data can be physically dispersed over many nodes, the access time for different data items may well be different which explains the term non-uniform data access. The term "Cache Coherent" refers to the fact that for all CPUs any variable that is to be used must have a consistent value. Therefore, it must be assured that the caches that provide these variables are also consistent in this respect. There are various ways to ensure that the caches of the CPUs are coherent. One is the snoopy bus protocol in which the caches listen in on transport of variables to any of the CPUs and update their own copies of these variables if they have them and are requested by a local CPU. Another way is the *directory memory*, a special part of memory which enables the caches to keep track of all the copies of variables and of their validity.

Presently, no commercially available machine uses the S-COMA scheme. By contrast, there are several popular ccNUMA systems (like Bull's bullx R422 series, HP Superdome, and SGI Ultraviolet) that are commercially available. An important characteristic of NUMA machines is the *NUMA*

factor. This factor shows the difference in latency for accessing data from a local memory location as opposed to a non-local one. Depending on the connection structure of the system the NUMA factor for various parts of a system can differ from part to part: accessing data from a neighbouring node will be faster than from a distant node in which possibly a number of stages of a crossbar must be traversed. So, when a NUMA factor is mentioned, this is mostly for the largest network cross-section, i.e., the maximal distance between processors.

Since the appearance of the multi-core processors the, ccNUMA phnomenon also manifests itself within processors with multiple cores: first and second level cache belong to a particular core and therefore when another core needs data that does not resides in its own cache, it has to retrieve it via the complete memory hierarchy of the processor chip. This is typically orders of magnitude slower than when it can be fetched from its local cache.

For all practical purposes we can classify these systems as being SM-MIMD machines also because special assisting hardware/software (such as a directory memory) has been incorporated to establish a single system image although the memory is physically distributed.

#### 8. Clusters

The adoption of clusters, collections of workstations/PCs connected by a local network, has virtually exploded since the introduction of the first Beowulf cluster in 1994. The attraction lies in the (potentially) low cost of both hardware and software and the control that builders/users have over their system. The interest for clusters can be seen for instance from the IEEE Task Force on Cluster Computing (TFCC) which reviews on a regular basis the current status of cluster computing (?). Also, books that describe how to build and maintain clusters have greatly added to their popularity (?, ?). As the cluster scene has become a mature and attractive market, large HPC vendors as well as many start-up companies have entered the field and offer more or less ready out-of-the-box cluster solutions for those groups that do not want to build their cluster from scratch (hardly anyone these days).

The number of vendors that sell cluster configurations has become so large that it is not possible to include all their products in this report. In addition, there is generally a large difference in the usage of clusters and they are more often used for *capability computing* while the integrated machines primarily are used for *capacity computing*. The first mode of usage meaning that the system is employed for one or a few programs for which no alternative is readily available in terms of computational capabilities. The second way of operating a system is in employing it to the full by using the most of its available cycles by many, often very demanding, applications and users. Traditionally, vendors of large supercomputer systems have learned

to provide for this last mode of operation as the precious resources of their systems were required to be used as effectively as possible. By contrast, Beowulf clusters used to be mostly operated through the Linux operating system (a small minority using Microsoft Windows) where these operating systems either missed the tools or these tools were relatively immature to use a cluster well for capacity computing. However, as clusters become on average both larger and more stable, there is a trend to use them also as computational capacity servers too, particularly because nowadays there is a plethora of cluster management and monitoring tools. In (?) the article is looked at some of the aspects that are necessary conditions for this kind of use like available cluster management tools and batch systems. The systems assessed then are now quite obsolete but many of the confusions are still valid: An important, but not very surprising conclusion was that the speed of the network is very important in all but the most compute bound applications. Another notable observation was that using compute nodes with more than 1 CPU may be attractive from the point of view of compactness and (possibly) energy and cooling aspects, but that the performance can be severely damaged by the fact that more CPUs have to draw on a common node memory. The bandwidth of the nodes is in this case not up to the demands of memory intensive applications.

As cluster nodes have become available with 4–8 processors where each processor also may have up to 12 processor cores, this issue has become all the more important and one might have to choose for capacity-optimised nodes with more processors but less bandwidth/processor core or capability-optimised nodes that contain less processors per node but have a higher bandwidth available for the processors in the node. This choice is not particular to clusters (although the phenomenon is relatively new for them), it also occurs in the integrated ccNUMA systems. Interestingly, as already remarked in the previous section, in clusters the ccNUMA memory access model is turning up now in the cluster nodes, as for the larger nodes, it is not possible anymore to guarantee symmetric access to all data items for all processor cores (evidently, for a core, a data item in its own local cache will be available more quickly than for a core in another processor).

Fortunately, there is nowadays a fair choice of communication networks available in clusters. Of course Gigabit Ethernet or 10 Gigabit Ethernet are always possible, which are attractive for economic reasons, but have the drawback of a high latency ( $\approx 10$ –40  $\mu$ s). Alternatively, there are networks that operate from user space at high speed and with a latency that approaches these of the networks in integrated systems. These will be discussed in section ??.

## 9. Processors

In comparison to 10 years ago the processor scene has become drastically different. While in the period 1980–1990, the proprietary processors and in particular the vector processors were the driving forces of the supercomputers of that period, to day that role has been taken over by common off-the-shelf processors. In fact there are only two companies left that produce vector systems while all other systems that are offered are based on RISC CPUs or x86-like ones. Therefore it is useful to give a brief description of the main processors that populate the present supercomputers and look a little ahead to the processors that will follow in the coming year. Still, we will be a bit more conservative in this section than in the description of the systems in general. The reason is processors are turned out at a tremendous pace while planning ahead for next generations takes years. We therefore tend to stick to the really existing components in this section or when already a  $\beta$  version of a processor is being evaluated.

The RISC processor scene has shrunken significantly in the last few years. The Alpha and PA-RISC processors have disappeared in favour of the Itanium processor product line and, interestingly, the MIPS processor line that appeared and disappeared again as they were used in the highly interesting SiCortex systems. Unfortunately SiCortex had to close down recently and with it the MIPS processors. In addition, the Itanium processor is not used in HPC anymore.

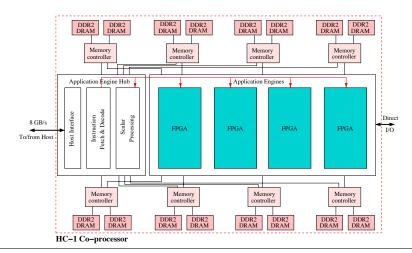

The disappearance of RISC processor families demonstrates a trend that is both worrying and interesting: worrying because the diversity in the processor field is decreasing severely and, with it, the choice for systems in this sector. On the other hand there is the trend to enhance systems having run-of-the-mill processors with special-purpose add-on processors in the form of FPGAs or other computational accelerators because their possibilities in performance, price level, power consumption, and ease of use has improved to a degree that they offer attractive alternatives for certain application fields.

The notion of "RISC processor" altogether has eroded somewhat in the sense that the processors that execute the Intel x86 (CISC) instruction set now have most of the characteristics of a RISC processor. Both the AMD and Intel x86 processors in fact decode the CISC instructions almost entirely into a set of RISC-like fixed-length instructions. Furthermore, both processor lines feature out-of-order execution, both are able to address and deliver results natively in 64-bit length, and the bandwidth from memory to the processor core(s) have become comparable to those of RISC/EPIC processors. A distinguishing factor is still the mostly much larger set of registers in the RISC processors.

Another notable development of the last few years are the placement of

Figure 9.8. Block diagram of an AMD Opteron Magny Cours processor.

multiple processor cores on a processor chip and the introduction of various forms of multi-threading. We will discuss these developments for each of the processors separately.

There are two processors one perhaps would expect in this section but are nevertheless not discussed: the Godson 3A and the Itanium Tukwila processors. The first processor, a Chinese one, based on the MIPS architecture, is not available in any machine that is marketed now or in the near future (it is to be succeeded by the Godson 3B early next year). The newest Itanium processor does not play a role anymore in the HPC scene and is therefore also omitted.

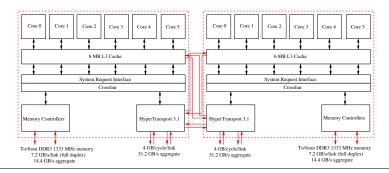

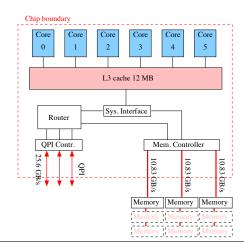

#### 9.1. AMD Magny-Cours

All AMD processors are clones with respect to Intel's x86 Instruction Set Architecture. The 12-core Opteron variant called "Magny-Cours" is no exception. It became available in March 2010. It is built with a feature size of 45 nm and in fact the chip is a package containing two modified 6-core Instanbul chips running at a maximum of 2.3 GHz in the 6176 SE variant. The two chips are connected through 16-bit HyperTransport 3.1 links to each other's L3 caches with a single-channel speed of 12.8 GB/s as shown in Figure ??.

The clock frequencies of the various parts of the chip are independent and different: while the processor operates at a speed of of 2.3 GHz the Hyper-Transport links run at 3.2 GHz and the four memory buses (two per 6-core chip) run at only 1.8 GHz, thus limiting the maximum bandwidth between memory and the chip to only 28.8 GB/s. AMD has made this choice to limit the power consumption although the new chips accommodate DDR3 memory at a speed of 1333 MHz which means that the bandwidth potentially could have been 42.7 GB/s. Like in the Istanbul processor, the Magny-Cours processor exploits the "HT Assist" function. HT Assist sets 1 MB in the L3 cache aside that contains the position and status of the cache lines in use on

Figure 9.9. Block diagram of an AMD Magny-Cours processor core.

the chip. In this way the change in status of cache variables does not have to be broadcast to all cores, but can simply be read from this part of the L3 cache, thus lowering the traffic in the interconnection fabric significantly. This setup is in fact an implementation of cache coherence via directory memory as explained in section ??. Comparison experiments with the earlier Shanghai processor have shown that HT Assist can be highly beneficial thanks to more bandwidth available for operand transfer. Because the number of cores has doubled with regard to the Istanbul processor the HT Assist function has become all the more important.

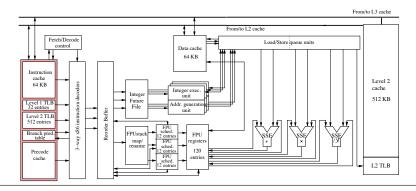

Although they use the x86 instruction set, the AMD processors can be regarded as full-fledged RISC processors: they support out-of-order execution, have multiple floating-point units, and can issue up to 9 instructions simultaneously. A block diagram of a processor core is shown in Figure ??. It is in effect identical to the Istanbul processor core. The six cores on the chip are connected by an on-chip crossbar. It also connects to the memory controller and, as said, to its companion chip and other processors on the board via HyperTransport.

The figure shows that a core has three pairs of Integer Execution Units and Address Generation Units that via an 32-entry Integer Scheduler takes care of the integer computations and of address calculations. Both the Integer Future File and the Floating-Point Scheduler are fed by the 72-entry Reorder Buffer that receives the decoded instructions from the instruction decoders. The decoding in the Opteron core has become more efficient than in the earlier processors: SSE instructions decode now into 1 micro-operation ( $\mu$ op) as are most integer and floating-point instructions. In addition, a piece of hardware, called the sideband stack optimiser, has been added (not shown in the figure) that takes care of the stack manipulations in the instruction stream, thus making instruction reordering more efficient, thereby increasing the effective number of instructions per cycle.

The floating-point units allow out-of-order execution of instructions via

the FPU Stack Map & Rename unit. It receives the floating-point instructions from the Reorder Buffer and reorders them if necessary before handing them over to the FPU Scheduler. The Floating-Point Register File is 120 elements deep on par with the number of registers as available in RISC processors <sup>1</sup>.

The floating-point part of the processor contains three units: Floating Add and Multiply units that can work in superscalar mode, resulting in two floating-point results per clock cycle and a unit handling "miscelaneous" operations, like division and square root. Because of the compatibility with Intel's processors, the floating-point units are also able to execute Intel SSE2/3 instructions and AMD's own 3DNow! instructions. However, there is the general problem that such instructions are not directly accessible from higher level languages, like Fortran 90 or C(++). Both instruction sets were originally meant for massive processing of visualisation data but are increasingly used for standard dense linear algebra operations.

Due to the shrinkage of technology to 45 nm each core can harbour a secondary cache of 512 KB. Because of the accommodation of DDR3 memory at a bus speed of 1333 MHz the total bandwidth (but with the limitation of the 1.8 GHz memory interface) a channel transports 7.2 GB/s or 14.4 GB/s per 6-core chip.

AMD's HyperTransport is derived from licensed Compaq technology and similar to that employed in HP/Compaq's former EV7 processors. It allows for "glueless" connection of several processors to form multi-processor systems with very low memory latencies. The Magny-Cours processor uses the fourth generation, HyperTransport 3.1, that transfers 12.8 GB/s 16-bit wide per unidirectional link. The HyperTransport interconnection possibility makes it highly attractive for building SMP-type clusters or to couple computational accelerators (see section ??) directly to the same memory as the standard processor.

#### 9.2. IBM POWER6

In the systems that feature IBM's supercomputer line, the p575 series, the nodes contain the POWER6 chip as the computational engine. This will change shortly and therefore we will also discuss the POWER7 processor in section ??, but as of this paper, the POWER6 is still the processor for IBM's high-end HPC systems. As compared to its predecessor, the POWER5+ there are quite some differences, both in the chip lay-out and in the two cores that reside on a chip. Figure ?? shows the layout of the cores, caches, and controllers on the chip. Already, there are significannt changes: instead

<sup>&</sup>lt;sup>1</sup> For the x86 instructions 16 registers in a flat register file are present instead of the register stack that is typical for Intel architectures.

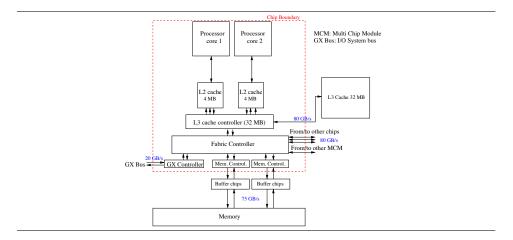

Figure 9.10. Diagram of the IBM POWER6 chip layout

of a 1.875 MB shared L2 cache, each core now has its own 4 MB 8-way set-associative L2 cache that operates at half the core frequency. In addition, there are 2 memory controllers that connect via buffer chips to the memory and, depending on the amount of buffer chips and data widths (both are variable) can have a data read speed  $\leq 51.2$  GB/s and a write speed of  $\leq 25.6$  GB/s, i.e., with a core clock cycle of 4.7 GHz up to 11 B/cycle for a memory read and half of that for a memory write. Furthermore, the separate busses for data and coherence control between chips are now unified with a choice of both kinds of traffic occupying 50% of the bandwidth or 67% for data and 33% for coherence control. The off-chip L3 cache has shrunk from 36 to 32 MB. It is a 16-way set-associative victim cache that operates at 1/4 of the clock speed.

Also the core has changed considerably. It is depicted in Figure ??. The

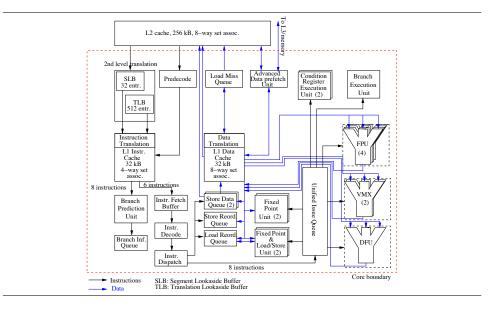

Figure 9.11. Block diagram of the IBM POWER6 core.

clock frequency has increased from 1.9 GHz in the POWER5+ to 4.7 GHz for the POWER6 (water cooled version), an increase of almost a factor 2.5 while the power consumption stayed in the same range of that of the POWER5+. This has partly come about by a technology shrink from a 90 nm to a 65 nm feature size. It also means that some features of the POWER5+ have disappeared. For instance, the POWER6 largely employs static instruction scheduling, except for a limited amount of floating-point instruction scheduling because some of these can sometimes be fit in empty slots left by division and square root operations. The circuitry required for dynamic instruction scheduling that thus could be removed has however been replaced by new units. Besides the 2 Fixed Point Units (FXUs) and the 2 Binary Floating-Point Units (BFUs) that were already present in the POWER5+, there os now a Decimal Floating-Point Unit (DFU) and a VMX unit, akin to Intel's SSE units for handling multimedia instructions. In fact, the VMX unit is inherited from the IBM PowerPC's Altivec unit. The Decimal Floating-Point Unit is IEEE 754R compliant. It is obviously for financial calculations and is hardly of consequence for HPC use. Counting only the operations of the BPUs both executing fused multipy-adds (FMAs), the theoretical peak performance in 64-bit precision is 4 flop/cycle or 18.8 Gflop/s/core. A Checkpoint Recovery Unit has been added that is able to catch faulty FXU and FPU (both binary and decimal) instruction executions and reschedule them for retrial. Because of the large variety of functional units, a separate Instruction Dispatch Unit ships the instructions that are ready for execution to the appropriate units, while a significant part of instruction decoding has been pushed into the Instruction Fetch Unit, including updating the Branch History Tables.

The BFUs not only execute the usual floating-point instructions like add, multiply, and FMA. They also take care of division and square root operations. A new phenomenon is that integer divide and multiply operations are also executed by the BFUs again saving on circuitry and therefore power consumption. In addition, these operations can be pipelined in this way and yield a result every 2 clock cycles.

The L1 data cache has been doubled in comparison to the POWER5+ and is now 64 KB like the L1 instruction cache. Both caches are 4-way set-associative.

The Simultaneous Multi-Threading (SMT) that was already present in the POWER5+ has been retained in the POWER6 processor and has been improved by a higher associativity of the L1 I and D caches and a larger dedicated L2 cache. Also, instruction decoding and dispatch are dedicated for each thread. By using SMT the cores are able to keep two process threads at work at the same time. The functional units get instructions for the functional units from any of the two threads whichever is able to fill a slot in an instruction word that will be issued to the functional units. In this

way a larger fraction of the functional units can be kept busy, improving the overall efficiency. For very regular computations single thread (ST) mode may be better because in SMT mode the two threads compete for entries in the caches, which may lead to trashing in the case of regular data access. Note that SMT is somewhat different from the "normal" way of multi-threading. In this case a thread that stalls for some reason is stopped and replaced by another process thread that is awoken at that time. Of course this takes some time that must be compensated for by the thread that has taken over. This means that the second thread must be active for a fair amount of cycles (preferably a few hundred cycles at least). SMT does not have this drawback but scheduling the instructions of both threads is quite complicated, especially where only very limited dynamic scheduling is possible.

Because the much higher clock cycle, and the fact that the memory DIMMs are attached to each chip, it is not possible anymore to maintain a perfect SMP behaviour within a 4-chip node, i.e., it matters whether data is accessed from a chip's own memory or from the memory of a neighbouring chip. Although the data is only one hop away there is a ccNUMA effect that one has to be aware of in multi-threaded applications.

#### 9.3. IBM POWER7

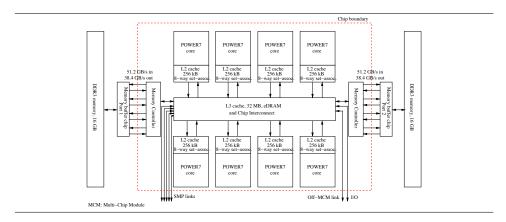

As already remarked before, at this moment IBM is not yet offering HPC systems with the POWER7 inside. This will however occur rather soon: POWER7-based HPC systems are expected by the end of 2011. In addition, Hitachi is already offering a variant of its SR16000 system with the POWER7 processor. So, it is appropriate to discuss this chip already in this report. Figure ?? shows the layout of the cores, caches, and memory controllers on the chip. The technology from which the chips are built is identical to

Figure 9.12. Diagram of the IBM POWER7 chip layout

that of the POWER6: 45 nm Silicon-On-Insulator but in all other aspects the differences with the former generation are large: firstly, the number of cores has quadrupled. Also the memory speed has increased from DDR2 to DDR3 via two on-chip memory controllers. As in earlier POWER versions the inbound and outbound bandwidth from memory to chip are different: 2 B/cycle in and 1.5 B/cycle out. With a bus frequency of 6.4 GHz and 4 in/out channels per controller this amounts to 51.2 GB/s inward and 38.4 GB/s outward. IBM asserts that an aggregate sustained bandwidth of  $\approx$ 100 GB/s can be reached. Although this is very high in absolute terms with a clock frequency of 3.5–3.86 GHz for the processors this is no luxury. Therefore it is possible to run the chip in so-called TurboCore mode. In this case four of the 8 cores are turned off and the clock frequency is raised to 4.14 GHz thus almost doubling the bandwidth for the active cores. As one core is capable of absorbing/producing 16B/cycle when executing a fused floating multiply-add operation the bandwidth requirement of one core at 4 GHz is already 64 GB/s. So, the cache hierarchy and possible prefetching are extremely important for a reasonable occupation of the many functional units.

Another new feature of the POWER7 is that the L3 cache has been moved onto the chip. To be able to do this IBM chose to implement the 32 MB L3 cache in embedded DRAM (eDRAM) instead of SRAM as is usual. eDRAM is slower than SRAM but much less bulky and because the cache is now on-chip, the latency is considerably lower (about a factor of 6). The L3 cache communicates with the L2 caches that are private to each core. The L3 cache is partitioned in that it contains 8 regions of 4 MB, one region per core. Each partition serves as a victim cache for the L2 cache to which it is dedicated and in addition to the other 7 L3 cache partitions.

Each chip features 5 10-B SMP links that supports SMP operation of up to 32 sockets.

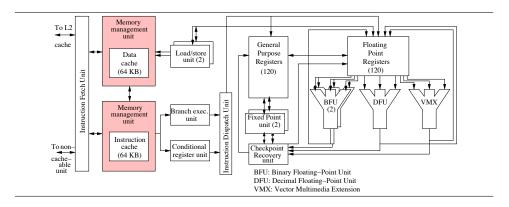

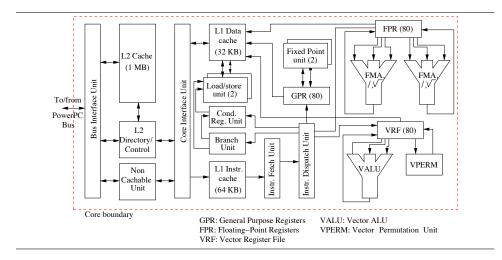

Also at the core level there are many differences with its predecessor. A single core is depicted in Figure ??. To begin with, the number of floating-point units is doubled to four, each capable of a fused multiply-add operation per cycle. Assuming a clock frequency of 3.86 GHz this means that a peak speed of 30.88 Gflop/s can be attained with these units. A feature that was omitted from the POWER6 core has been re-implemented in the POWER7 core: dynamic instruction scheduling assisted by the load and load reorder queues. As shown in Figure ?? there are two 128-bit VMX units. One of them executes vector instructions akin to the x86 SSE instructions. However there is also a VMX permute unit that can order non-contiguous operands such that the VMX execute unit can handle them. The instruction set for the VMX unit is an implementation of the AltiVec instruction set that is also employed in the PowerPC processors. There are also similarities with the POWER6 processor: the core contains a Decimal floating-point unit

Figure 9.13. Block diagram of the IBM POWER7 core.

(DFU) and a checkpoint recovery unit that can re-schedule operations that have failed for some reason.

Another difference that cannot be shown is that the cores now support 4 SMT threads instead of 2. This will be very helpful for the large amounts of functional units to be kept busy. Eight instructions can be taken from the L1 instruction cache. The instruction decode unit can handle 6 instructions simultaneously while 8 instructions can be dispatched every cycle to the various functional units.

The POWER7 core has elaborate power management features that reduces the power usage for parts that are idle for some time. There are two power-saving mode: *nap* mode and *sleep* mode. In the former the caches and TLBs stay coherent to re-activate quickly. In sleep mode, however, the caches are purged and the clock turned off. Only the minimum voltage to maintain the memory contents is applied. Obviously the wake-up time is longer in this case but the power saving can be significant.

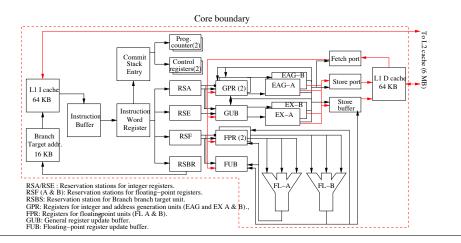

# 9.4. IBM PowerPC 970MP processor

A number of IBM systems are built from JS21 blades, the largest being the Mare Nostrum system at the Barcelona Supercomputing Centre. On these blades a variant of the large IBM PowerPC processor family is used, the dual core PowerPC 970MP. It is a series of dual-core processors the fastest of which has a clock cycle of 2.2 GHz. A block diagram of a processor core is given in Figure ??.

Figure 9.14. Block diagram of the IBM PowerPC 970MP core.

A peculiar trait of the processor is that the L1 instruction cache is two times larger than the L1 data cache, 64 against 32 KB. This is explained partly by the fact that up to 10 instructions can be issued every cycle to the various execution units in the core. Apart from two floating-point units that perform the usual dyadic operations, there is an AltiVec vector facility with a separate 80-entry vector register file, a vector ALU that performs (fused) multiply/add operations, and a vector permutation unit that attempts to order operands such that the vector ALU is used optimally. The vector unit was designed for graphics-like operations but works quite nicely on data for other purposes as long as access is regular and the operand type agrees. Theoretically, the speed of a core can be 13.2 Gflop/s/core when both FPUs turn out the results of a fused multiply-add and the vector ALU does the same. One PowerPC 970MP should therefore have a theoretical peak performance of 26.4 Gflop/s. The floating-point units also perform square-root and division operations.

Apart from the floating-point and vector functional units, two integer fixed-point units and two load/store units are present in addition to a conditional register unit and a branch unit. The latter uses two algorithms for branch prediction that are applied according to the type of branch to be taken (or not). The success rate of the algorithms is constantly monitored. Correct branch prediction is very important for this processor as the pipelines of the functional units are quite deep: from 16 for the simplest integer operations to 25 stages in the vector ALU. So, a branch miss can be very costly. The L2 cache is integrated and has a size of 1 MB. To keep the load/store latency low, hardware-initiated prefetching from the L2 cache is possible and 8 oustanding L1 cache misses can be tolerated. The operations

are dynamically scheduled and may be out-of-order. In total 215 operations may be in flight simultateously in the various functional units, also due to the deep pipelines.

The two cores on a chip have common arbitration logic to regulate the data traffic from and to the chip. There is no third level cache between the memory and the chip on the board housing them. This is possible because of the moderate clock cycle and the rather large L2 cache.

#### 9.5. IBM BlueGene processors

In the last few years two BlueGene types of systems have become available: the BlueGene/L and the BlueGene/P, the successor of the former. Both feature processors based on the PowerPC 400 processor family.

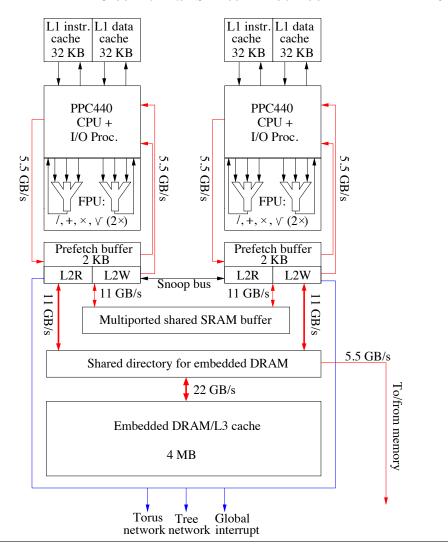

#### BlueGene/L processor

This processor is in fact a modified PowerPC 440 processor, which is made especially for the IBM BlueGene family. It runs at a speed of 700 MHz. The modification lies in tacking on floating-point units (FPUs)that are not part of the standard processor but can be connected to the 440's APU bus. Each FPU contains two floating-point functional units capable of performing 64-bit multiply-adds, divisions and square-roots. Consequently, the theoretical peak performance of a processor core is 2.8 Gflop/s. Figure ?? shows the embedding of two processor cores on a chip. As can be seen from the figure, the L2 cache is very small: only 2 KB divided in a read and a write part. In fact it is a prefetch and store buffer for the rather large L3 cache. The bandwidth to and from the prefetch buffer is high, 16 B/cycle to the CPU and 8 B/cycle to the L2 buffer. The memory resides off-chip with a maximum size of 512 MB. The data from other nodes are transported through the L2 buffer, bypassing the L3 cache in first instance.

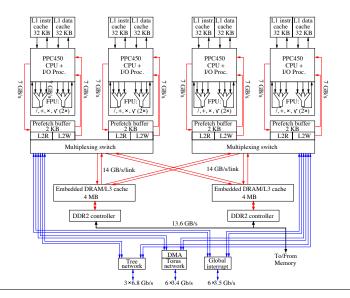

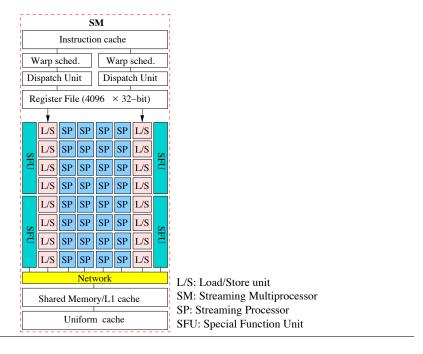

#### BlueGene/P processor

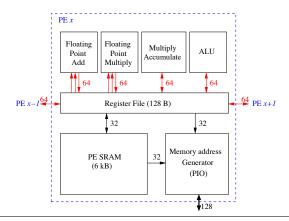

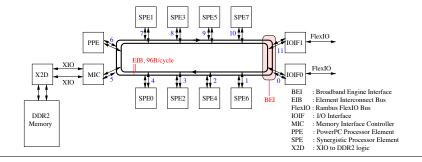

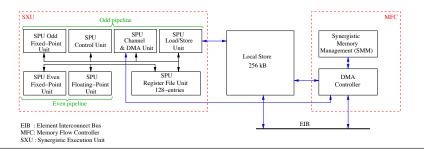

Like the BlueGene/L processor the BlueGene/P processor is based on the PowerPC core, the PowerPC 450 in this case at a clock frequency of 850 MHz and with similar floating-point enhancements as applied to the PPC 440 in the BlueGene/L. The BlueGene/P node contains 4 processor cores which brings the peak speed to 13.6 Gflop/s/node. The block diagram in Figure ?? shows some details. As can be seen from the Figure the structure of the core has not changed much with respect to the BlueGene/L. The relative bandwidth from the L2 cache has been maintained: 16 B/cycle for reading and 8 B/cycle for writing. In contrast to the BlueGene/L, the cores operate in SMP mode through multiplexing switches that connect pairs of cores to the two 4 MB L3 embedded DRAM chips. So, the L3 size has doubled. Also, the memory per node has increased to 2 GB from 512 MB.

Figure 9.15. Block diagram of an IBM BlueGene/L processor chip.

#### 9.6. Intel Xeon

Two variants of Intel's Xeon processors are employed presently in HPC systems (clusters as well as integrated systems): The Nehalem EX, officially the X7500 chip series, and the Westmere EP, officially the X5600 series. Although there is a great deal of communality they are sufficiently different to discuss both processors separately.

Figure 9.16. Block diagram of an IBM BlueGene/P processor chip.

#### Nehalem EX

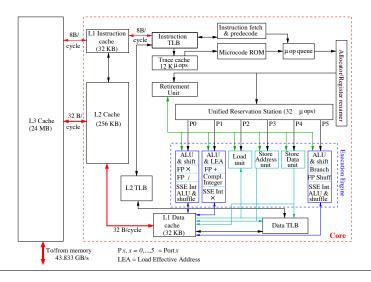

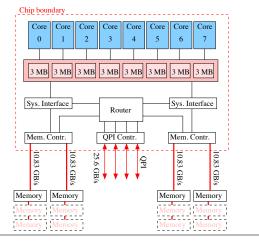

The Nehalem EX became available in March 2010 or, more officially, the X7500 series of processors can be regarded as a heavy-duty server extension of the earlier Nehalem EP (X5500) processor. As such it has double the amount of cores, eight, and the number of QPI links also doubled to four to enable the connection to other processors on a server board. In addition the bandwidth is raised because the number of memory interfaces has increased from three to four. As the bandwidth per memory channel is 10.833 GB/s the aggregate bandwidth of the chip is 43.3 MB/s. The Nehalem EX is employed in SGI's Altix UV systems and a variety of products from cluster vendors. Below we show the block diagram of the processor core which is in fact identical to that of the Nehalem EP and built in the same 45 nm technology. A block diagram of the core is given in Figure ?? while the layout of an 8-core chip is shown in Figure ??

To stay backwards compatible with the x86 (IA-32) Instruction Set Architecture, which comprises a CISC instruction set, Intel developed a modus in which these instructions are split in so-called micro operations ( $\mu$ -ops) of fixed length that can be treated in the way RISC processors do. In fact the  $\mu$ -ops constitute a RISC operation set. The price to be payed for this much more efficient instruction set is an extra decoding stage. Branch prediction has been improved and also a second level TLB cache been added.

As in the earlier Core architecture 4  $\mu$ -ops/cycle and some macro-instructions as well as some  $\mu$ -ops can be fused, resulting in less instruction handling, easier scheduling and better instruction throughput because these fused op-

Figure 9.17. Block diagram of an Intel Nehalem processor core.

Figure 9.18. Diagram of a Nehalem EX processor.

erations can be executed in a single cycle. In the Nehalem, 2 additional  $\mu$ -ops can be fused in comparison to the Core architecture.

As can be seen in Figure ?? the processor cores have an execution trace cache which holds partly decoded instructions of former execution traces that can be drawn upon, thus foregoing the instruction decode phase that might produce holes in the instruction pipeline. The allocator dispatches the decoded instructions, the  $\mu$ -ops, to the unified reservation station that can issue up to 6  $\mu$ -ops/cycle to the execution units, collectively called the Execution Engine. Up to 128  $\mu$ -ops can be in flight at any time. Figure ?? shows that port 0 and port 5 drive two identical Integer ALUs as well as Integer SSE units. Port 0, 1, and 5 take care of the various floating-point operations.

The two integer Arithmetic/Logical Units at port 0 and 5 are kept simple in order to be able to run them at twice the clock speed. In addition there is an ALU at port 1 for complex integer operations that cannot be executed within one cycle. The floating-point units also contain additional units that execute the Streaming SIMD Extensions 4 (SSE4) repertoire of instructions, an instruction set of more than 190 instructions, that was initially meant for vector-oriented operations like those in multimedia, and 3-D visualisation applications, but is also an advantage for regular vector operations as occur in dense linear algebra. The length of the operands for these units is 128 bits. The Intel compilers have the ability to address the SSE4 units. This enables in principle much higher floating-point performance. Port 2, 3, and 4 serve the Load unit, the Store Address unit, and the Store Data unit, respectively.

A notable enhancement that cannot be shown in the figures is that the Nehalem (again) supports multi-threading, much in the style of IBM's simultaneous multithreading, and is called Hyperthreading by Intel. Hyperthreading was earlier introduced in the Pentium 4 but disappeared in later Intel processors because the performance gain was very low. Now with a much higher bandwidth and larger caches speedups of more than 30% for some codes have been observed with Hyperthreading. Another feature that cannot be shown is the so-called Turbo Mode. This means that the clock cycle can be raised from its nominal speed (2.91 GHz for the fastest variant) by steps of 133 MHz to over 3 GHz as long as the thermal envelope of the chip is not exceeded. So, when some cores are relatively idle other cores can take advantage by operating at a higher clock speed.

The L1 caches have the same size as in the Nehalem's predecessor, but the L2 cache is much smaller: 256 KB instead of 6 MB. It is much faster however and able to deliver requested data in 10 cycles or less. The Nehalems feature a common L3 cache that is used by all eight cores in the EX version. Each core has its own section of 3 MB but when data is not found in the section of a core the other sections can be searched for the missing data item(s).

The L3 cache is inclusive which means that it contains all data that are in the L2 and L1 cache. The consequence is that when a data item cannot be found in the L3 cache it is also not in any of the caches of the other cores, and therefore one need not search them.

In Figure ?? it can be noticed that apart from the first bank of memory of  $\leq 32$  GB also a second and third bank are depicted, represented by dashed boxes. This means that it is indeed possible to have up to 96 GB of memory/processor. However, this can only be done at the expense of the memory bus speed: for one bank it is 1333 MB/s, for two banks it is 1066 MB/s, and for three banks only 800 MB/s. So, the latter two options may be chosen for instance for database systems that benefit from a large memory that not needs to be at the very highest speed. For HPC purposes, however, configurations with only one memory bank/processor will usually be offered.

#### Westmere EP

The Westmere EP (X5600 series) is a 32 nm technology shrink of the Nehalem EP chip. The smaller feature size is used to place 6 cores on a die. The fastest variant, the X5690 has a clock cycle of 3.46 GHz at 130 W. The structure of the core is the same as in the Nehalem processors (see Figure ??) but there are slight differences in the instruction set for the Advanced Encryption Standard (AES). The new instructions, among which is a carryless multiplication, are said to speed up the en/decryption rate by a factor of three. Also the Westmere EP supports the use of 1 GB pages. The packaging on the chip is, apart from the number of cores, identical to that of the Nehalem EP chip with exception of the shared L3 cache. The size of this is halved from 24 MB to 12 MB. The chip layout is depicted in Figure ??

## 9.7. The SPARC processors